使用蝕刻工藝可以提升半導體封裝的質量與可靠性的方法有以下幾個方面:

優化蝕刻工藝參數:在進行蝕刻過程中,合理選擇刻蝕液的成分、濃度、溫度、時間等參數,以及控制刻蝕液的流速和攪拌方式,可以有效提高蝕刻的均勻性和準確性,從而提升封裝的質量。通過實驗和模擬優化工藝參數,可以獲得更好的蝕刻效果。

表面預處理:在進行蝕刻之前,對待刻蝕的表面進行適當的預處理,如清洗、去除氧化層等,以確保目標材料表面的純凈性和一致性。這樣可以避免蝕刻過程中出現不均勻的刻蝕和不良的質量。

控制蝕刻深度和侵蝕率:蝕刻的深度和侵蝕率是影響封裝質量和可靠性的重要因素。通過精確控制蝕刻時間、濃度和波動等參數,可以實現準確控制蝕刻深度,并避免過度蝕刻或局部侵蝕。這可以確保封裝器件的尺寸和形狀符合設計要求,并提高可靠性。

監控蝕刻過程:在蝕刻過程中,通過實時監測和記錄蝕刻深度、表面形貌和刻蝕速率等關鍵參數,可以及時發現蝕刻過程中的異常情況,避免不良的蝕刻現象。這有助于提高封裝的質量并保證一致性。

綜合考慮材料特性、工藝要求和設備條件等因素,選擇合適的蝕刻方法和優化工藝參數,可以有效提升半導體封裝的質量與可靠性。蝕刻技術如何實現半導體封裝中的仿真設計!廣東半導體封裝載體規范

蝕刻是一種半導體封裝器件制造過程,用于制造電子元件的金屬和介質層。然而,蝕刻過程會對器件的電磁干擾(EMI)性能產生一定的影響。

封裝器件的蝕刻過程可能會引入導線間的電磁干擾,從而降低信號的完整性。這可能導致信號衰減、時鐘偏移和誤碼率的增加。且蝕刻過程可能會改變器件內的互聯距離,導致線路之間的電磁耦合增加。這可能導致更多的互模干擾和串擾。此外,蝕刻可能會改變器件的地線布局,從而影響地線的分布和效果。地線的布局和連接對于電磁干擾的抑制至關重要。如果蝕刻過程不當,地線的布局可能會受到破壞,導致電磁干擾效果不佳。還有,蝕刻過程可能會引入輻射噪聲源,導致電磁輻射干擾。這可能對其他器件和系統產生干擾,影響整個系統的性能。

為了減小蝕刻對半導體封裝器件的EMI性能的影響,可以采取以下措施:優化布線和引腳布局,減小信號線之間的間距,降低電磁耦合。優化地線布局和連接,確保良好的接地,降低地線回流電流。使用屏蔽材料和屏蔽技術來減小信號干擾和輻射。進行EMI測試和分析,及早發現和解決潛在問題。

總之,蝕刻過程可能會對半導體封裝器件的EMI性能產生影響,但通過優化設計和采取相應的措施,可以減小這種影響,提高系統的EMI性能。安徽半導體封裝載體價格咨詢新一代封裝技術對半導體產業的影響和前景。

在射頻和微波應用中,半導體封裝載體的性能研究至關重要。以下是生產過程中注意到的一些可以進行研究的方向和關注點:

封裝材料選擇:封裝材料的介電性能對信號傳輸和封裝性能有很大影響。研究不同材料的介電常數、介質損耗和溫度穩定性,選擇合適的封裝材料。

封裝結構設計:射頻和微波應用中,對信號的傳輸和耦合要求非常嚴格,封裝結構設計需要考慮信號完整性、串擾、功率耗散等因素。研究封裝結構的布線、分層、引線長度等參數的優化。

路由和布線規劃:在高頻應用中,信號的傳輸線要考慮匹配阻抗、信號完整性和串擾等問題。研究信號路由和布線規劃的較優實踐,優化信號的傳輸性能。

封裝功耗和散熱:對于高功率射頻和微波應用,功耗和散熱是關鍵考慮因素。研究封裝的熱導率、散熱路徑和散熱結構,優化功率的傳輸和散熱效果。

射頻性能測試:封裝載體在射頻應用中的性能需要通過測試進行驗證。研究射頻性能測試方法和工具,評估封裝載體的頻率響應、S參數、噪聲性能等指標。

射頻封裝可靠性:射頻和微波應用對封裝的可靠性要求高,因為封裝載體可能在高溫、高功率和高頻率的工作條件下長時間運行。研究封裝材料的熱膨脹系數、疲勞壽命和可靠性預測方法,提高封裝的可靠性。

要利用蝕刻技術實現半導體封裝的微尺度結構,可以考慮以下幾個步驟:

1. 設計微尺度結構:首先,根據需求和應用,設計所需的微尺度結構。可以使用CAD軟件進行設計,并確定結構的尺寸、形狀和位置等關鍵參數。

2. 制備蝕刻掩膜:根據設計好的結構,制備蝕刻掩膜。掩膜通常由光刻膠制成,可以使用光刻技術將掩膜圖案轉移到光刻膠上。

3. 蝕刻過程:將制備好的掩膜覆蓋在待加工的半導體基片上,然后進行蝕刻過程。蝕刻可以使用濕蝕刻或干蝕刻技術,具體選擇哪種蝕刻方式取決于半導體材料的特性和結構的要求。在蝕刻過程中,掩膜將保護不需要被蝕刻的區域,而暴露在掩膜之外的區域將被蝕刻掉。

4. 蝕刻后處理:蝕刻完成后,需要進行蝕刻后處理。這包括清洗和去除殘留物的步驟,以確保結構的表面和性能的良好。

5. 檢測和測試:對蝕刻制備的微尺度結構進行檢測和測試,以驗證其尺寸、形狀和性能是否符合設計要求。可以使用顯微鏡、掃描電子顯微鏡和電子束測試設備等進行表征和測試。

通過以上步驟,可以利用蝕刻技術實現半導體封裝的微尺度結構。這些微尺度結構可以用作傳感器、微流體芯片、光電器件等各種應用中。蝕刻技術為半導體封裝帶來更高的集成度!

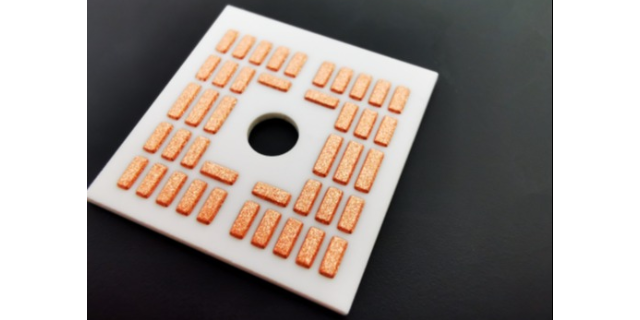

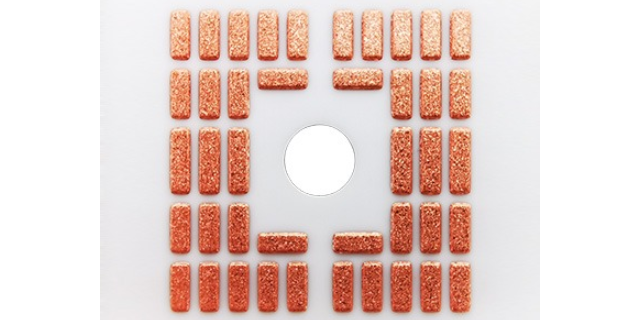

高密度半導體封裝載體的研究與設計是指在半導體封裝領域,針對高密度集成電路的應用需求,設計和研發適用于高密度封裝的封裝載體。以下是高密度半導體封裝載體研究與設計的關鍵點:

1. 器件布局和連接設計:在有限封裝空間中,優化器件的布局和互聯結構,以實現高密度封裝。采用新的技術路線,如2.5D和3D封裝,可以進一步提高器件集成度。

2. 連接技術:選擇和研發適合高密度封裝的連接技術,如焊接、焊球、微小管等,以實現高可靠性和良好的電氣連接性。

3. 封裝材料和工藝:選擇適合高密度封裝的先進封裝材料,如高導熱材料、低介電常數材料等,以提高散熱性能和信號傳輸能力。

4. 工藝控制和模擬仿真:通過精確的工藝控制和模擬仿真,優化封裝過程中的參數和工藝條件,確保高密度封裝器件的穩定性和可靠性。

5. 可靠性測試和驗證:對設計的高密度封裝載體進行可靠性測試,評估其在不同工作條件下的性能和壽命。

高密度半導體封裝載體的研究與設計,對于滿足日益增長的電子產品對小尺寸、高性能的需求至關重要。需要綜合考慮器件布局、連接技術、封裝材料和工藝等因素,進行優化設計,以提高器件的集成度和性能,同時確保封裝載體的穩定性和可靠性。蝕刻技術推動半導體封裝的小型化和輕量化!陜西半導體封裝載體誠信合作

半導體封裝技術的基本原理。廣東半導體封裝載體規范

蝕刻工藝在半導體封裝器件中的使用可能會對介電特性產生一定影響,具體影響因素包括材料選擇、蝕刻劑和蝕刻條件等。

1. 材料選擇對介電特性的影響:不同材料的介電特性會受到蝕刻工藝的影響。例如,蝕刻過程中可能引入表面缺陷或氧化層,對材料的介電常數和介電損耗產生影響。因此,研究不同材料的蝕刻工藝對介電特性的影響是重要的。

2. 蝕刻劑和蝕刻條件對介電特性的影響:蝕刻劑的選擇和蝕刻條件會直接影響蝕刻過程中的表面形貌和化學成分,從而影響材料的介電特性。研究不同蝕刻劑和蝕刻條件對介電特性的影響,可以為優化蝕刻工藝提供指導。

3. 蝕刻工藝對絕緣材料界面和界面態的影響:在封裝器件中,絕緣材料常常扮演重要角色。蝕刻工藝可能引入界面態或改變絕緣材料界面的結構和化學成分,從而影響介電特性。

4. 蝕刻工藝對介電層表面質量的影響:在封裝器件中,常常涉及介電層的制備和加工。蝕刻工藝可能影響介電層的表面質量,例如引入表面粗糙度或缺陷。

綜上所述,研究蝕刻工藝對半導體封裝器件介電特性的影響,需要考慮材料選擇、蝕刻劑和蝕刻條件、絕緣材料界面和界面態以及介電層表面質量等因素。這些研究有助于優化蝕刻工藝,提高封裝器件的介電性能。廣東半導體封裝載體規范